Virtual Memory I

(Usage hints for this presentation)

IT Systems, Summer Term 2026

Dr.-Ing. Matthes Elstermann

1. Introduction

1.1. Core Questions

- What is virtual memory?

- How can RAM be (de-) allocated flexibly under multitasking?

- How does the OS keep track for each process what data resides where in RAM?

- How does the OS manage the exchange of data between secondary storage and RAM under multitasking?

(Based on Chapter 6 of (Hailperin 2019))

1.2. Learning Objectives

- Explain mechanisms and uses for virtual memory

- Including principle of locality and page fault handling

- Including paging, swapping, and thrashing

- Perform address translation with page tables

- Apply page replacement with FIFO, LRU, Clock

1.3. Previously on OS …

1.3.1. Retrieval Practice

- How are processes and threads related?

- What happens when an interrupt is triggered?

1.3.2. Recall: RAM in Hack

1.4. Big Picture

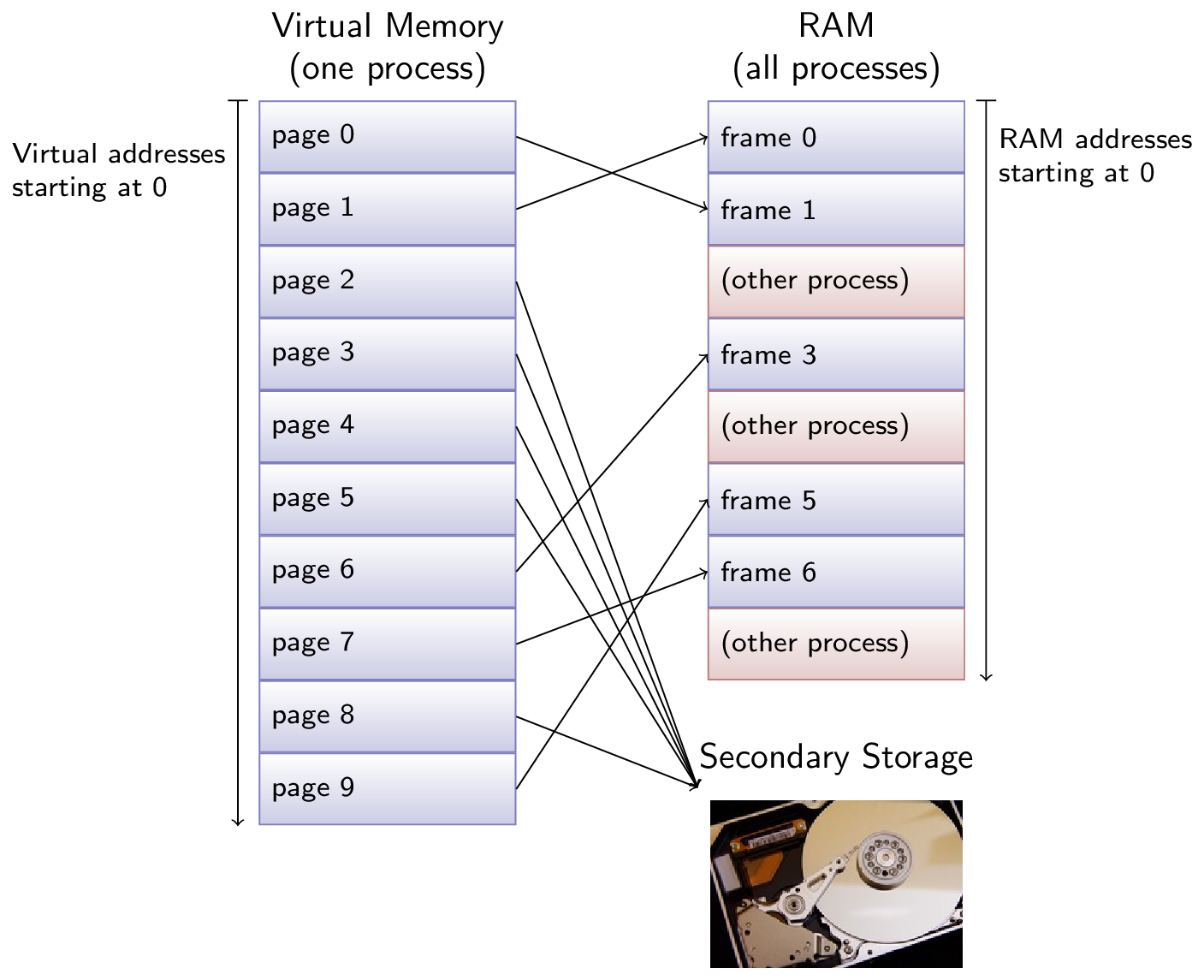

- Each process with own virtual address space

- Virtual address space and RAM split into equal-sized chunks

- Pages in virtual address space, frames in RAM

- Virtual address space and RAM split into equal-sized chunks

Physical memory split among all processes

![Big picture for virtual memory]()

OS maintains page table per process

Valid Frame# 1 1 1 0 0 X 0 X 0 X 0 X 1 3 1 6 0 X 1 5

1.4.1. Drawing for Page Tables

The page table

Figure © 2016 Julia Evans, all rights reserved; from julia's drawings. Displayed here with personal permission.

1.4.2. Big Picture of VM

1.5. Different Learning Styles

- The bullet point style may be exceptionally challenging for this presentation

- You may prefer

this short text

(PDF version)

- It provides an alternative view on

- Topics of Introduction

- Topics of section Paging

- It provides an alternative view on

- Besides, Chapter 6 of (Hailperin 2019) is about virtual memory

Agenda

- Part 1

- Part 2

2. Paging and Address Translation

2.1. MMU and TLB

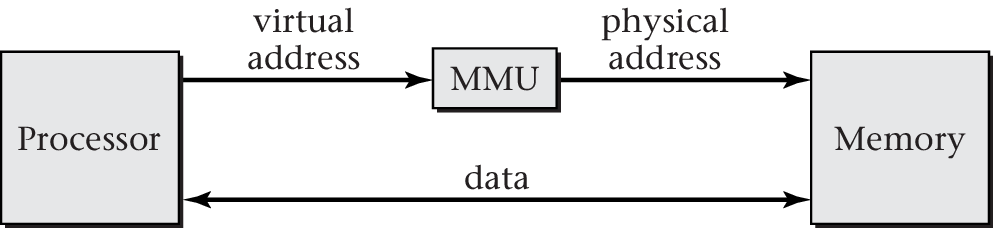

Address translation by Memory Management Unit

Latency: Access of page table before RAM access

![Figure 6.4 of (Hailperin 2019)]()

“Figure 6.4 of (Hailperin 2019)” by Max Hailperin under CC BY-SA 3.0; converted from GitHub

- Improvement: Caching

- Special cache, Translation Lookaside Buffer (TLB), for page table entries

- Recently used translations of page numbers to frame numbers

- MMU searches in TLB first to build physical address

- Note: Search for page, not entire virtual address

- If not found (TLB miss): Page table access

- Note: Context switch may invalidate TLB → Overhead

- (Beyond class: (Hailperin 2019) explains address space identifiers)

- Special cache, Translation Lookaside Buffer (TLB), for page table entries

2.2. Page Fault Handler

Pages may or may not be present in RAM

- Access of virtual address whose page is in RAM is called

page hit

- (Access = CPU executes machine instruction referring to that address)

- Otherwise, page miss

- Access of virtual address whose page is in RAM is called

page hit

- Upon page miss, a page fault is triggered

2.3. Use of Page Table

“Translation of hierarchical address with lookup in page table” by Max Lütkemeyer and Jens Lechtenbörger under CC BY-SA 4.0; from GitLab

- Virtual

addressinterpreted as hierarchical object- Page number, determined by most significant bits of

address- Below, 10 bits; simple (unrealistic) example

- Offset, remaining bits of

address= byte number within its page- Below, also 10 bits; typically, 12 bits in practice

- Page number, determined by most significant bits of

2.3.1. Offset as Pointer into Range

“Address translation with offset in covered address range” by Max Lütkemeyer and Jens Lechtenbörger under CC BY-SA 4.0; from GitLab

2.3.2. Address Translation Example (1/3)

Task: Translate virtual address to physical address

Subtask: Translate bits for page number to bits for frame number

- Suppose

- Pages and frames have a size of 1 KiB (= 1024 B)

- 15-bit physical addresses for RAM locations

- 20-bit virtual addresses, as on previous slides

First, derive following pieces of information

Size of physical address space: 215 B = 32 KiB

Size of virtual address space: 220 B = 1024 KiB = 1 MiB

- 10 bits are used for offsets (as 210 B = 1024 B)

- Remaining 5 physical bits enumerate 25 = 32 frames

- Remaining 10 virtual bits enumerate 210 = 1024 pages

2.3.3. Address Translation Example (2/3)

- Hierarchical interpretation of addresses

- 20-bit virtual address: 10 bits for page number 10 bits for offset

- 15-bit physical address: 5 bits for frame number 10 bits for offset

Task: Translate virtual address 42

42 = 0000000000 0000101010

- Page number = 0000000000 = 0

- Offset = 0000101010 = 42

Based on page table: Page 0 is located in frame 1

- In general, address translation exchanges

page number with

frame number

- Here, 0 with 1

- In general, address translation exchanges

page number with

frame number

Thus, 42 is located in frame 1

- Physical address 00001 0000101010 = 1066 (= 1024 + 42)

2.3.4. Address Translation Example (3/3)

- Based on page table

- Page 6 is located in frame 3

- Page 6 contains addresses

between 6*1024 = 6144 and 6*1024+1023 = 7167

- Consider virtual address 7042

- 7042 = 0000000110 1110000010

- Page number = 0000000110 = 6

- Offset = 1110000010 = 898

- Replace page number 6 with frame number 3

- 7042 is located in frame 3

- Physical address 00011 1110000010 = 3970 (= 3*1024 + 898)

- 7042 = 0000000110 1110000010

- Consider virtual address 7042

2.4. Self-Study Tasks

Answer the following questions in Learnweb.

Suppose that 32-bit virtual addresses with 4 KiB pages are used.

- How many bits are necessary to number all bytes within pages?

- How many pages does the address space contain? How many bits are necessary to enumerate them?

- Where within a 32-bit virtual address can you “see” the page number?

Bibliography

License Information

Source files are available on GitLab (check out embedded submodules) under free licenses. Icons of custom controls are by @fontawesome, released under CC BY 4.0.

Except where otherwise noted, the work “Virtual Memory I”, © 2017-2026 Jens Lechtenbörger, is published under the Creative Commons license CC BY-SA 4.0.